與門

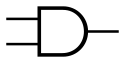

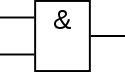

外觀

| 基本邏輯閘 | |

| 緩衝 | 非 |

| 與 | 與非 |

| 或 | 或非 |

| 異或 | 同或 |

| 蘊含 | 蘊含非 |

| 輸入 | 輸出 | |

| A | B | A AND B |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

與門(英語:AND gate)是數碼邏輯中實現邏輯與的邏輯門,功能見右側真值表。僅當輸入均為高電壓(1)時,輸出才為高電壓(1);若輸入中至多有一個高電壓時,則輸出為低電壓。換句話說,與門的功能是得到兩個二進制數的最小值,而或門的功能是得到兩個二進制數的最大值。

概述

[編輯]下列包括邏輯門的3種符號:形狀特徵型符號(ANSI/IEEE Std 91-1984)、IEC矩形國標(中國大陸)符號(IEC 60617-12)和不再使用的DIN符號(DIN 40700)。其他的邏輯門符號見邏輯門符號表。

| 表達式 | 符號 | 功能表 | 繼電器邏輯 | |||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ANSI/IEEE Std 91-1984 | IEC 60617-12 | DIN 40700 | ||||||||||||||||||

|

|

|

|

| ||||||||||||||||

若與門的其中一個輸入取反則成為禁門(INHIBIT logic gate,INHIBITOR)。

實現

[編輯]與門是基本的邏輯門,因此大多數半導體製造商都會生產這種集成電路。例如,在TTL集成電路7408和CMOS集成電路4081均由四個2輸入與門構成。

|

與門通常用n通道(NMOS)或p通道(PMOS)的MOSFET實現。數碼輸入a與b引起輸出F,這和與門的功能一致。

備選方案

[編輯]

如果沒有現成的與門,則可用與非門{x and y=(x nand y)nand (x nand y)}或或非門{(x and y=(x nor x)nor(y nor y)}來實現,因為與非門和或非門被認為是「通用的邏輯門電路」[1],因為通過這兩種門電路可以實現其他所有門電路的功能。若用與非門實現與門,則將一個與非門的兩個輸入結在一起,然後在其輸入端接入一個雙輸入的與非門;若用或非門實現與門,則將兩個輸入接在一起的或非門分別作另外一個或非門的兩個輸入,然後在後者的輸入接一個輸入接在一起的或非門。異或門也可用來實現與門,但很少使用。

參見

[編輯]參考文獻

[編輯]- ^ Mano, M. Morris and Charles R. Kime. Logic and Computer Design Fundamentals, Third Edition. Prentice Hall, 2004. p. 73.