電子設計自動化

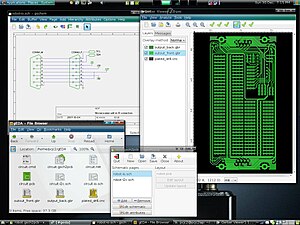

电子设计自动化(英語:Electronic design automation,縮寫:EDA)是指利用计算机辅助设计(CAD)软件,来完成超大规模集成电路(VLSI)芯片[來源請求]的功能设计、综合、验证、物理设计(包括布局、布线、版图、设计规则检查等)等流程的设计方式。

历史与发展

[编辑]在电子设计自动化出现之前,设计人员必须手工完成集成电路的设计、布线等工作,这是因为当时所谓集成电路的复杂程度远不及现在。工业界开始使用几何学方法来制造用于电路光绘(photoplotter)的胶带。[來源請求]

到了1970年代中期,开发人员尝试将整个设计过程自动化,而不仅仅满足于自动完成掩膜草图。第一个电路布局、布线工具研发成功。设计自动化研討會(Design Automation Conference)在这一时期被创立,旨在促进电子设计自动化的发展。[1]

电子设计自动化发展的下一个重要阶段以卡弗尔·米德(Carver Mead)和琳·康維于1980年发表的论文《超大规模集成电路系统导论》(Introduction to VLSI Systems)为标志。这一篇具有重大意义的论文提出了通过编程语言来进行芯片设计的新思想。[2]如果这一想法得到实现,芯片设计的复杂程度可以得到显著提升。这主要得益于用来进行集成电路逻辑仿真、功能验证的工具的性能得到相当的改善。随着计算机仿真技术的发展,设计项目可以在构建实际硬件电路之前进行仿真,芯片布局、布线对人工设计的要求降低,而且软件错误率不断降低。直至今日,尽管所用的语言和工具仍然不断在发展,但是通过编程语言来设计、验证电路预期行为,利用工具软件综合得到低抽象级(或称“后端”)物理设计的这种途径,仍然是数字集成电路设计的基础。

从1981年开始,电子设计自动化逐渐开始商业化。1984年的设计自动化会议(Design Automation Conference)上还举办了第一个以电子设计自动化为主题的销售展览。Gateway设计自动化在1986年推出了一种硬件描述语言Verilog,这种语言在现在是最流行的高级抽象设计语言。[3][4]1987年,在美国国防部的资助下,另一种硬件描述语言VHDL被创造出来。现代的电子设计自动化设计工具可以识别、读取不同类型的硬件描述。[5]根据这些语言规范产生的各种仿真系统迅速被推出,使得设计人员可对设计的芯片进行直接仿真。后来,技术的发展更侧重于逻辑综合。

进入21世纪之后,一方面,三家大EDA公司(Synopsys、Cadence、Mentor)通过多次并购整合,完善设计全流程,奠定了三巨头竞争格局。另一方面,EDA公司开始深入制造领域,发展出了OPC等制造EDA的工具以及可制造性设计(DFM)工具。同时,晶圆厂成为了EDA的深度用户,不仅在制造方面需要使用EDA工具,在标准单元库、SRAM设计上都需要使用。此外,领先晶圆厂每两年开发一代工艺,其中EDA的整套设计流程需要在新工艺上验证。EDA也开始在早期工艺研发中介入,帮助解决更复杂的设计规则以及种种难题。晶圆厂提供的Signoff签核流程决定了设计公司设计出的芯片能否在晶圆制造厂顺利生产。而Signoff签核的主要工具就是EDA,可以说EDA是架起了设计与制造沟通的桥梁。同时,先进工艺不断迭代也驱动了EDA的创新。可见,此时此刻EDA在产业链已经有着举足轻重的作用。[6]

目前的数字集成电路的设计都比较模块化(参见集成电路设计、设计收敛(Design closure)和设计流(Design flow (EDA))。半导体器件制造工艺需要标准化的设计描述,高抽象级的描述将被编译为信息单元(cell)的形式。设计人员在进行逻辑设计时尚无需考虑信息单元的具体硬件工艺。利用特定的集成电路制造工艺来实现硬件电路,信息单元就会实施预定义的逻辑或其他电子功能。半导体硬件厂商大多会为它们制造的元件提供“元件库”,并提供相应的标准化仿真模型。相比数字的电子设计自动化工具,模拟系统的电子设计自动化工具大多并非模块化的,这是因为模拟电路的功能更加复杂,而且不同部分的相互影响较强,而且作用规律复杂,电子元件大多没有那么理想。Verilog AMS就是一种用于模拟电子设计的硬件描述语言。[7]此外,设计人员可以使用硬件验证语言来完成项目的验证工作目前最新的发展趋势是将集描述语言、验证语言集成为一体,典型的例子有SystemVerilog。[8][9]

随着集成电路规模的扩大、半导体技术的发展,EDA的重要性急剧增加。这些工具的使用者包括半导体器件制造中心的硬件技术人员,他们的工作是操作半导体器件制造设备并管理整个工作车间。一些以设计为主要业务的公司,也会使用电子设计自动化软件来评估制造部门是否能够适应新的设计任务。电子设计自动化工具还被用来将设计的功能导入到类似现场可编程逻辑门阵列的半定制可程式邏輯裝置,或者生产全定制的特殊應用積體電路。

現況

[编辑]現今數位電路非常模組化(參見集成电路设计、设计收敛、設計流程 (EDA)),產線最前端將設計流程標準化,把設計流程區分為許多「細胞」(cells),而暫不考慮技術,接著細胞則以特定的集成電路技術實現邏輯或其他電子功能。製造商通常會提供組件庫(libraries of components),以及符合標準模擬工具的模擬模型給生產流程。類比EDA工具較不模組化,因為它需要更多的功能,零件間需要更多的互動,而零件一般說較不理想。

在電子產業中,由於半導體產業的規模日益擴大,EDA扮演越來越重要的角色。使用這項技術的廠商多是從事半导体器件制造的代工製造商,以及使用EDA模擬軟體以評估生產情況的設計服務公司。EDA工具也應用在现场可编程逻辑门阵列的程序設計上。

如今的集成电路,从系统架构开始,落实到功能的定义和实现,最终实现整个芯片的版图设计与验证,是一项复杂的系统工程,集成了人类智慧的最高成果。以华为2020年最新的7nm麒麟990芯片来说,其中集成了103亿颗晶体管,若没有EDA輔助,设计这样复杂的电路并保证良率是无法想象的。可见EDA這套工具,赋能了集成电路设计与制造的创新,当之无愧的站在了产业链的顶端。[6]

未来发展趋势

[编辑]目前,EDA在国际市场上已经发展成为了相对成熟的产业,而每年增长率只有10%左右。[6]但有业内人士分析认为,这并不代表日后发展的机会在变小,在未来 EDA 的发展趋势可能有:[6]

- AI赋能

- EDA上云

- 异构集成

另一方面,由於美國對華科技禁令的影響,中國將逐漸放棄自美國引進全套EDA服務,加上開發方向的轉變,產業發展轉而投向中國自研EDA的高成長市場[10],為了保住中國的利潤,美國幾大EDA公司甚至展開了竞争,為此大舉投資中國EDA新勢力並設立各自的合作據點。[11]科技產業的變化,也帶動起步中的中國EDA品牌的往新的大方向前進,並隨著技術落實而逐漸獲利後,EDA為美國壟斷的格局將會出現變化。[12]

重點軟體分類

[编辑]設計

[编辑]- 高级综合(或行为综合、算法综合)——高级设计描述(例如在C/C++中)转换为RTL。

- 逻辑综合-将RTL设计描述(例如用Verilog或VHDL编写)转换为逻辑门的离散netlist。

- 原理图捕获-用于标准单元数字,模拟,rf类捕获CIS在Orcad由Cadence和ISIS在Proteus

- 布局——通常是由模式驱动的布局,比如在Orcad中的Cadence布局,在Proteus中的ARES布局

仿真

[编辑]- 晶体管仿真——对原理图/布局行为的低层晶体管仿真,精确到器件级别。

- 逻辑仿真——对RTL或门网表的数字行为进行数字仿真,精确到布尔级别。

- 行为仿真——对设计的架构操作进行高层仿真,精确到周期级别或接口级别。

- 硬件仿真——使用特殊目的硬件仿真拟议设计的逻辑,有时可以插入到系统中替代尚未构建的芯片;这被称为电路仿真。

- 技术CAD仿真和分析基础过程技术。器件的电气特性直接从器件物理推导。

分析及驗證

[编辑]- 功能验证:确保逻辑设计与规格相符,并正确执行任务。包括通过仿真、仿真和原型的动态功能验证。

- RTL Linting:检查代码是否遵循语法、语义和样式等编码规则。

- 时钟域交叉验证(CDC检查):类似于Linting,但这些检查/工具专门用于检测和报告由于使用多个时钟域而可能出现的数据丢失、元稳定性等问题。

- 形式验证,也称为模型检查:尝试通过数学方法证明系统具有某些期望的属性,并且某些不希望发生的效果(如死锁)不会发生。

- 等效性检查:对芯片的RTL描述和综合后的门网表进行算法比较,以确保逻辑层面的功能等效。

- 静态时序分析:以输入无关的方式分析电路的时序,从而找到所有可能输入的最坏情况。

- 布局提取:从拟议的布局开始,计算每条导线和器件的(近似)电气特性。通常与上述静态时序分析一起使用,以估算完成芯片的性能。

- 电磁场求解器,或称场求解器,直接求解麦克斯韦方程,适用于集成电路和PCB设计中的特定问题。它们以精确度较高、但速度较慢而闻名。

- 物理验证,PV:检查设计是否可以物理制造,生成的芯片是否不存在任何阻止功能的物理缺陷,并且能满足原始规格。

製造製備

[编辑]- 掩模数据准备或MDP——生成实际的光刻掩模,用于物理制造芯片。

- 芯片修整,包括定制设计标记和结构,以提高布局的可制造性。后者的例子包括密封环和填充结构。

- 生成带有测试图案和对准标记的掩模布局。

- 布局到掩模准备:通过图形操作增强布局数据,如分辨率增强技术(RET)——提高最终光刻掩模的质量的方法。还包括光学邻近效应修正(OPC)或逆光刻技术(ILT)——在芯片制造时补偿衍射和干涉效应。

- 掩模生成——从分层设计生成平面掩模图像。

- 自动测试图案生成或ATPG——系统地生成模式数据,以尽可能多地测试逻辑门和其他组件。

- 自测试或BIST——安装自包含的测试控制器,自动测试设计中的逻辑或存储器结构。

- 功能安全

- 功能安全分析,系统地计算设计中的失效率(FIT)和诊断覆盖度指标,以满足所需的安全完整性级别的合规性要求。

- 功能安全综合,通过在结构化元素(模块、RAM、ROM、寄存器文件、FIFO)中增加可靠性增强来改善故障检测/容错能力。这包括(但不限于)添加错误检测和/或纠正代码(汉明码)、冗余逻辑用于故障检测和容错(双重/三重)以及协议检查(接口奇偶校验、地址对齐、节拍计数)。

- 功能安全验证,运行故障试验,包括向设计中插入故障并验证安全机制对已覆盖的故障作出适当反应。

参见

[编辑]参考文献

[编辑]- ^ Access Years of Vital Information. DAC. [2013-01-05]. (原始内容存档于2013-09-29).

- ^ Carver Mead, Lynn Conway. Introduction to VLSI Systems. Addison-Wesley Pub (Sd). 1980. ISBN 978-0201043587.

- ^ Donald E. Thomas, Philip R. Moorby. 硬件描述语言Verilog(第四版,英文名:The Verilog Hardware Description Language (Fouth Edition)). 清华大学出版社. 2001. ISBN 7-900635-36-X.

- ^ 夏宇闻. Verilog基本知识 (上). 电子产品世界. 2002, (19).

- ^ Mixed VHDL/Verilog Synthesis. University of Edinburgh. [2012-08-15]. (原始内容存档于2013-06-11).

- ^ 6.0 6.1 6.2 6.3 韩明. EDA发展要秉持“战略冗余”观念 (PDF). 中国电子报 (总第4358期) (中国电子报社). 2020年6月19日 [2020年6月19日]. (原始内容 (PDF)存档于2020年6月22日).

- ^ 夏宇闻. 一种高层次的支持模拟和数模混合信号电路与系统设计的语言Verilog-A/AMS. 电子技术应用. 1999, 25 (8).

- ^ 1800-2009 - IEEE Standard for SystemVerilog--Unified Hardware Design, Specification, and Verification Language. IEEE. [2012-08-13]. (原始内容存档于2012-05-07).

- ^ SystemVerilog Overview. SystemVerilog Official Website. [2012-08-24]. (原始内容存档于2012-05-02).

- ^ 存档副本. [2021-03-14]. (原始内容存档于2021-07-25).

- ^ 存档副本. [2021-03-14]. (原始内容存档于2021-07-25).

- ^ 存档副本. [2021-03-14]. (原始内容存档于2021-07-25).

- Steven M. Rubin. Computer Aids for VLSI Design. Static Free Software. [2013-01-05]. (原始内容存档于2020-09-24).

- Lavagno, Martin, and Scheffer. Electronic Design Automation For Integrated Circuits Handbook. CRC Press. 2006. ISBN 0-8493-3096-3.

- Thomas Lengauer. Combinatorial Algorithms for Integrated Circuit Layout. Teubner Verlag. 1997. ISBN 3-519-02110-2.

- Dirk Jansen; et al. The Electronic Design Automation Handbook. Kluwer Academic Publishers. 2003. ISBN 1-4020-7502-2.